## Sixth Semester B.E. Degree Examination, Dec.2014/Jan.2015 **Microelectronics Circuits**

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, selecting atleast THREE questions from Part-A and TWO from Part-B.

## PART - A

Derive an expression for drain current of a MOSFET in different regions of operation. 1

Design a circuit of Fig.Q.1(b), so that the transistor operates at  $I_D = 0.4$ mA and  $V_D = +0.5$ V. The NMOS transistor has  $V_t = 0.7V$ ,  $\mu_n C_{ox} = 100 \mu A/V^2$ ,  $L = 1 \mu m$ , and  $W = 32 \mu m$ . Neglect channel length modulation effect ( $\lambda = 0$ ).

- c. Draw the small signal circuit model of MOSFET when  $|VSB| \neq 0$  and explain briefly. (ie including the body effect). (04 Marks)

- d. For the common drain amplifier stage, draw the small signal equivalent circuit and drive expressions for A<sub>v</sub>, A<sub>vo</sub>, G<sub>v</sub>, R<sub>in</sub> and R<sub>out</sub>. (06 Marks)

- 2 Compare and explain the important characteristics of NMOS and NPN transistors.

(05 Marks)

- With a neat circuit diagram and equations explain the basic BJT current steering circuits. (05 Marks)

- c. For the high frequency equivalent circuit of common source amplifier in Fig.Q.2(c), find the midband voltage gain  $A_m = V_o/V_{sig}$  and upper 3dB frequency  $f_H$  using open circuit time constants.

Where  $R_L^1 = 3.3 \text{K}\Omega$ ;  $R_{sig} = 100 \text{K}\Omega$ ;  $R_{in} = 420 \text{K}\Omega$ ;  $C_{gs} = C_{gd} = 1P_f$ ,  $g_m = 4m \text{ A/V}$ .

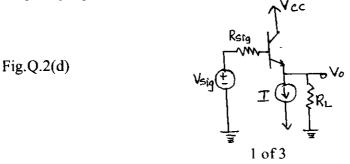

d. For the emitter follower biased by a constant current source I, shown in Fig.Q.2(d), draw the (02 Marks) high frequency equivalent circuit clearly naming all the components:

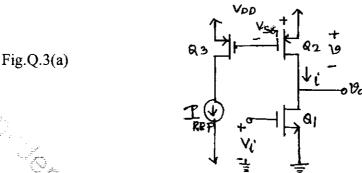

3 a. A CMOS common source amplifier shown in Fig.Q.3(a) is fabricated with W/L = 100  $\mu$ m/1.6  $\mu$ m for all transistors. With Kn' = 90  $\mu$ A/V<sup>2</sup>, Kp1' = 30  $\mu$ A/V<sup>2</sup>, IREF = 100 $\mu$ A, V<sub>An</sub> = 8 V/ $\mu$ m and V<sub>AP</sub> = 12 V/ $\mu$ m, determine the following quantities  $g_{m1}$ ,  $r_{o1}$ ,  $r_{o2}$ , A<sub>vo</sub>. (06 Marks)

- b. Draw the MOS cascade amplifier circuit with current source biasing. With the help of small signal equivalent circuit. Show that the cascading increases magnitude of open circuit voltage gain from A<sub>0</sub> to A<sub>0</sub><sup>2</sup>. (06 Marks)

- c. Write short notes on cascade MOS current mirror circuit.

(04 Marks)

- d. Find  $A_o$  for an NMOS transistor fabricated in a 0.4 $\mu$ m CMOS process for which  $Kn' = 200\mu A/V^2$ , and  $VA' = 20V/\mu m$ . The transistor has a 0.4 $\mu$ m channel length and is operated with an overdrive voltage of 0.25V. What must be W for NMOS transistor to operate at  $I_D = 100\mu A$ ? Also find  $f_o$  and  $g_m$ . (04 Marks)

- 4 a. Explain the operation of MOS differential pair with a differential input voltage and derive the range of differential input for differential mode of operation. (08 Marks)

- b. Prove that  $A_{CM} = \frac{-r_{o4}}{2R_{SS}} \times \frac{1}{1 + g_{m3} r_{o3}}$  for the active loaded MOS differential amplifier.

(08 Marks)

- c. For the BJT differential amplifier having  $\beta = 100$ , matched to 10% or better, and areas that are matched to 10% or better, along with collector resistors that are matched to 2% or better, find  $V_{OS}$ ,  $I_B$  and  $I_{OS}$ . The dc bias current is  $100\mu A$ . (04 Marks)

- 5 a. Explain the operation of MOSFET as a linear amplifier. (05 Marks)

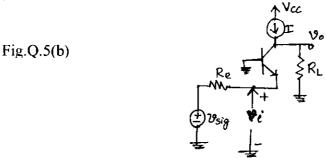

- b. For the common base amplifier shown in Fig.Q.5(b) draw the small signal equivalent circuit and hence derive an expression for R<sub>in</sub>, R<sub>out</sub> and A<sub>vo</sub>. (06 Marks)

- c. A MOS differential amplifier is operated at a total current of 0.8mA, using transistors with W/L ratios of 100,  $K_{n'} = \mu_{n}$   $C_{ox} = 0.2$  mA/V<sup>2</sup>,  $V_{A} = 20V$  and  $R_{D} = 5K\Omega$ . Find  $V_{OV} = (V_{GS} V_{t})$ ,  $g_{m}$ ,  $r_{o}$ ,  $A_{d}$ . (05 Marks)

- d. Explain channel length modulation effect of MOSFET.

(04 Marks)

## PART - B

6 a. What are the four properties of negative feed back? Briefly explain about each property.

(08 Marks)

b. For the series-shunt feedback ideal amplifier find A<sub>f</sub>, R<sub>if</sub> and R<sub>of</sub>.

(06 Marks)

- c. Discuss the method of frequency compensation for modifying open loop gain A(s) so that the closed loop amplifier is stable, by introducing a new pole in transfer function at sufficiently low frequency.

(06 Marks)

- 7 a. Draw the circuit diagram of basic difference amplifier and derive an expression for the output voltage V<sub>out</sub> and differential input resistance R<sub>id</sub>. (05 Marks)

- b. Show that the gain bandwidth product of an inverting amplifier is smaller than that of a non inverting amplifier. (05 Marks)

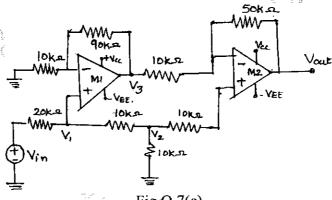

- c. Find the output voltage of the circuit, assuming Op. Amp M1 has DC open loop gain of  $1 \times 10^5$  and a bandwidth of 10 rad/sec., op amp M<sub>2</sub> is an ideal op, amp (Ref.Fig.Q.7(c)).

(06 Marks)

Fig.Q.7(c)

d. Write a note on use of op-amp in sample and hold circuit.

(04 Marks)

- 8 a. Draw the basic structure of CMOS inverter and explain the voltage transfer characteristic of CMOS inverter (08 Marks)

- b. Consider a CMOS inverter fabricated in a 0.25 $\mu$ m process for which  $C_{ox} = 6fF/\mu m^2$ ,  $\mu_n C_{ox} = 115\mu A/V^2$ ,  $\pi_p C_{ox} = 30\mu A/V^2$ ,  $V_{tn} = -V_{tp} = 0.4V$  and  $V_{DD} = 2.5V$ . The W/L ratio of  $Q_N$  is 0.375  $\mu$ m/0.25 $\mu$ m and for  $Q_p$  is 1.125 $\mu$ m/0.25 $\mu$ m. The equivalent capacitance value is 6.25fF. Find  $t_{PHL}$ ,  $t_{PLH}$  and  $t_p$ .

- c. Explain with neat circuit diagrams about pull-up and pull-down networks used in CMOS logic circuits. (06 Marks)

\* \* \* \* \*